|

|

|||||||||||

|

|

|||||||||||

|

|

|||||||||||

|

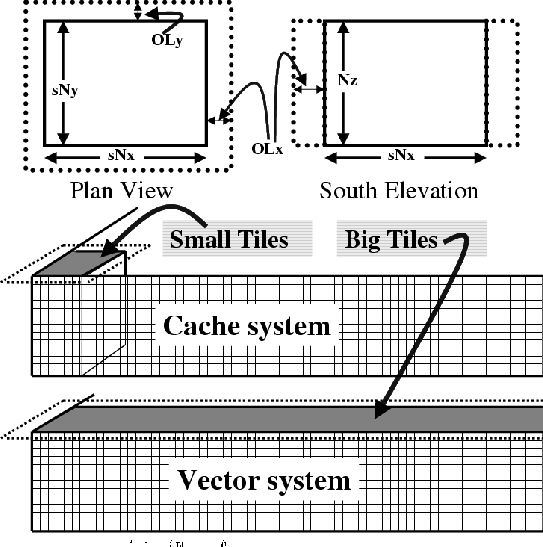

Next: 4.2.10 Summary Up: 4.2 WRAPPER Previous: 4.2.8 Communication primitives Contents 4.2.9 Memory architectureThe WRAPPER machine model is aimed to target efficiently systems with highly pipelined memory architectures and systems with deep memory hierarchies that favor memory reuse. This is achieved by supporting a flexible tiling strategy as shown in figure 4.8. Within a CPU computations are carried out sequentially on each tile in turn. By reshaping tiles according to the target platform it is possible to automatically tune code to improve memory performance. On a vector machine a given domain might be sub-divided into a few long, thin regions. On a commodity microprocessor based system, however, the same region could be simulated use many more smaller sub-domains.

Next: 4.2.10 Summary Up: 4.2 WRAPPER Previous: 4.2.8 Communication primitives Contents mitgcm-support@mitgcm.org |

||||